随着集成电路工艺制程技术的不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,半导体工艺的特征尺寸不断缩小,晶体管的栅、源和漏有源区的尺寸也会相应缩小,而它们的等效串联电阻会相应变大,从而影响电路的速度。为了改善等效串联电阻,半导体业界先后发展出金属硅化物工艺技术Polycide和Salicide。

最先出现的金属硅化物工艺技术是Polycide工艺技术,Polycide工艺技术是为了改善多晶硅栅的等效串联电阻和接触孔的接触电阻,Polycide工艺技术仅仅在多晶硅栅上形成金属硅化物,源和漏有源区不会形成金属硅化物,所以它没有办法改善晶体管源和漏有源区的等效串联电阻和接触孔的接触电阻。为了改善晶体管源和漏有源区的等效串联电阻和接触孔的接触电阻而发展出Salicide工艺技术,Salicide工艺技术不仅在多晶硅栅上形成金属硅化物,而且在源和漏有源区也会形成金属硅化物,它同时改善晶体管的栅、源和漏有源区的等效串联电阻和接触孔的接触电阻。

本文摘选自《集成电路制造工艺与工程应用》第三章第五节的内容,这部分内容简单介绍了Polycide工艺技术、Salicide工艺技术和SAB工艺技术的原理,并以纳米级工艺形成ESD器件和Non-Salicide器件为例介绍SAB和Salicide工艺技术的工程应用。

1.1金属硅化物工艺技术

首先引起半导体业界重视的多晶硅栅的等效串联电阻,多晶硅栅的电阻率比较高,虽然栅等效串联电阻不会损害电路的直流特性,但是它会影响器件的高频特性。在CMOS工艺制程中,多晶硅栅的厚度是2.5kÅ~3kÅ,对于厚度为3kÅ的多晶硅栅,它的方块电阻高达36ohm/sq。对于一个宽度W=10um和沟道长度L=0.35um的器件,栅极的串联电阻是1028.6ohm/sq,器件栅极等效串联电阻会造成非常大的RC延时。为了降低多晶硅栅和有源区的方块电阻,金属硅化物(Silicide)工艺技术被开发出来并广范应用在半导体工艺制程 。Silicide是由金属和硅经过化学反应形成的一种金属化合物,其导电特性介于金属和硅之间。最先应用于半导体工艺制程的Silicide材料是多晶硅金属硅化物(Polycide),Polycide是指仅仅在多晶硅栅上形成金属硅化物,源和漏有源区不会形成金属硅化物。业界利用多晶硅和Polycide的双层结构代替多晶硅栅,从而降低多晶硅的方块电阻。Polycide的材料是硅化钨(WSi2),对于厚度1KÅ的多晶硅和1.5KÅ的Polycide的双层结构的方块电阻大约是3ohm/sq。

当半导体工艺的特征尺寸缩小到深亚微米以下时,晶体管源和漏有源区的尺寸宽度不断缩小导致器件的有源区串联电阻不断增大,另外后端互连接触孔的尺寸也不断缩小,随着接触孔尺寸的不断缩小,单个接触孔的接触电阻也不断升高,对于0.25μm工艺技术平台的接触孔,它的尺寸达到0.32μm以下,单个接触孔的接触电阻已经升高到200ohm以上了。为了降低有源区的串联电阻和接触电阻,也需要在有源区上形成金属硅化物,该技术是利用金属(Ti、Co和NiPt等)与直接接触的有源区和多晶硅栅的硅反应形成Silicide,金属不会与接触的SiO2、Si3N4和SiON等介质材料发生反应,所以Silicide能够很好地与有源区和多晶硅栅对准,把同时在有源区和多晶硅栅上形成Silicide的技术称为自对准金属硅化物(Self Aligned Silicide - Salicide)。

1.2 Polycide工艺技术

Polycide工艺技术是指在器件的栅极上形成金属硅化物薄膜,栅极由一定厚度的多晶硅薄膜和金属硅化物薄膜组成。Polycide工艺技术仅仅会在多晶硅栅上形成金属硅化物减小栅极的电阻,而不会改变有源区的电阻。

Polycide工艺技术主要应用在特征尺寸在亚微米的集成电路制造工艺。Polycide工艺技术的工艺实现过程是首先通过LPCVD淀积多晶硅薄膜,然后再通过LPCVD在多晶硅上淀积金属硅化物WSi2薄膜。WSi2反应的气体源是SiH2Cl2和WF2,反应的温度是550℃,它的化学反应式是:7SiH2Cl2 2WF6 2WSi2 3SiF4 14HCl。WSi2的热稳定性非常好,它的阻值并不会随着工艺温度而改变。

硅和金属硅化物存在相互扩散的问题,对于Polycide工艺技术,淀积的是WSi2金属,多晶硅和WSi2的相互扩散可以促使多晶硅和WSi2更好的结合,并不会影响器件性能和栅极的电性。另外,Polycide只淀积在Poly层上,多晶硅栅的掺杂类型不会影响Polycide的阻值,所以设计上不会区分n型或者p型多晶硅电阻。

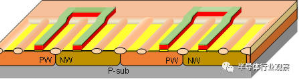

为了更好的理解Polycide工艺技术,请参考第四章第一节亚微米工艺中Polycide的工艺步骤。如图3-103所示,是亚微米及以上工艺制程技术形成Polycide的剖面图。

图3-103 亚微米及以上工艺制程技术形成Polycide的剖面图

1.3 Salicide工艺技术

Salicide工艺技术是在标准的CMOS工艺技术的基础上增加硅金属化的相关工艺步骤,Salicide工艺步骤是完成源和漏离子注入后进行的。形成Salicide的基本工艺步骤是首先利用物理气相淀积(Physical Vapor Deposition - PVD)在多晶硅栅和有源区上淀积一层金属(Ti,Co和NiPt等)。然后进行两次快速热退火处理(RTA)以及一次选择性湿法刻蚀处理,最终在多晶硅表面和有源区表面形成Salicide,金属硅化物包括TiSi2,CoSi2和NiPtSi等薄膜。金属Ti,Co或NiPt不会跟介质材料反应形成金属硅化物,只会与直接接触的多晶硅和有源区反应形成金属硅化物。与Polycide不同的是Salicide工艺技术会在多晶硅和有源区同时形成Salicide,降低它们的方块电阻和接触电阻,在设计上可以得到更小串联电阻,减小RC延时,提高电路的速度。

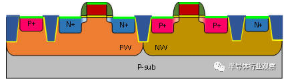

为什么需要两次RTA呢?以Ti-Salicide工艺为例,首先淀积一层Ti薄膜,然后再淀积一层TiN薄膜覆盖在Ti薄膜上,淀积TiN薄膜的目的是防止Ti在快速热退火处理时流动。第一次RTA-1的温度比较低,只有450~650℃,Ti只会与有源区或者多晶硅的硅反应形成高阻态的金属硅化物Ti2Si,它是体心斜方晶系结构,它是C49相,Ti不会和氧化硅反应生成金属硅化物,所以可以利用选择性湿法刻蚀去除表面的TiN薄膜和氧化硅上没有反应的Ti薄膜。第二次RTA-2温度很高,最低也要750℃,有的工艺平台要求高达950℃,RTA-2可以将C49相的高阻态金属硅化物Ti2Si转化为低阻的C54相金属硅化物TiSi2,C54相是面心斜方晶系结构,它的热力学特性很好,非常稳定。如果只通过一次RTA生成低阻的金属硅化物TiSi2,那么这个步骤的RTA的工艺温度会很高,在如此高温的环境下,硅可以沿着TiSi2的晶粒边界进行扩散,导致氧化硅边界上面的TiSi2过度生长,湿法刻蚀无法去除氧化物上的金属硅化物,而造成短路。如图3-104所示,是经过两次不同温度的RTA工艺步骤,只在源、漏和栅上形成Salicide。如图3-105所示,是只经过一次高温的RTA,在STI和侧墙上也形成Salicide,造成短路。

图3-104在源、漏和栅上形成Salicide

图3-105在STI和侧墙上形成Salicide

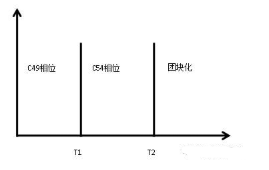

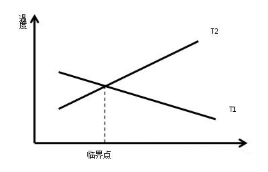

如图3-106所示,是Salicide工艺技术中两次RTA工艺的温度相位图。第一次RTA-1使金属与硅反应形成相位C49的高阻态金属硅化物Ti2Si、Co2Si或者Ni2PtSi,它的反应温度小于T1,T1(Ti)> T1(Co)> T1(NiPt)。然后用湿法刻蚀(刻蚀的酸是NH4OH和H2O2)去除氧化物上未反应的金属,防止桥连短路。第二次RTA-2需要更高的温度T2,把相位C49转化为C54的低阻金属硅化物生成TiSi2/CoSi2/ NiPtSi2,T2(Ti)> T2(Co)> T2(NiPt)。

图3-106 Salicide工艺技术中两次RTA工艺的温度相位图

Ti-Salicide有一个致命的缺点,随着Salicide厚度的降低或者线宽的减小,Ti-Salicide由C49相位转化为C54相位的临界温度T1会升高,而C54相位发生团块化的临界温度T2反而会降低,以致于会出现T1=T2的临界点,甚至会出现T2小于T1的情况,如图3-107所示,是T1和T2随silicide厚度或线宽变化图。如果出现T2小于T1的情况,Ti-Salicide 出现C49相位后就会直接发生团块化,根本就不存在C54相位这个区间,也就是根本找不到降低金属硅化物电阻的工艺条件,所以只有大尺寸的工艺才会采用Ti-Salicide工艺技术,例如特征尺寸为0.5µm~0.25µm的工艺技术。而Co-Salicide可以有效避免这种直接发生团块化现象,所以特征尺寸为0.18µm~65nm的工艺技术都采用Co-Salicide工艺技术。另外由于特征尺寸为65nm以下的工艺技术需要特别考虑热量的问题,所以选择NiPt-Salicide工艺技术,因为NiPt-Salicide工艺技术的RTA工艺温度比Co-Salicide工艺低。

图3-107 T1和T2随Silicide厚度或线宽变化图

另外硅和金属还存在互扩散的问题,对于Ti-Salicide工艺技术,淀积的金属是Ti,在形成硅化物的过程中,硅是主要扩散物,在边缘处可以参与反应的硅相对来说会少一点,所以边缘形成的金属硅化物的厚度就会相应变薄,那么边缘的薄层电阻就会相应变大,表现出来的特性就是金属硅化物的边缘的电阻较大。对于线宽为0.18µm以下的工艺技术,这种特性会非常严重。除了边界处金属硅化物电阻增大的问题,另外硅会扩散到金属上,引起的桥接问题。由于硅扩散到金属中的速度大于金属扩散到硅中的速度,所以金属硅化物不仅会在金属与硅的直接接触面形成,还会在氧化物上形成造成桥接,例如STI和侧墙上。虽然STI和侧墙上Ti金属并不与硅直接接触。当初始的硅金属化反应发生在纯N2气氛中进行时,可以阻止硅化物在横向上的生长。另外金属Co和NiPt可以有效的避免上述效应,这是0.18µm ~ 65nm工艺技术选择用Co代替Ti的原因。

Co-Salicide对线宽控制比Ti-Salicide好,RTA1的温度是300~370℃,形成C49相位的金属硅化物Co2Si,当温度大约为500℃时Co2Si转化为CoSi,然后在700℃或者更高的温度下形成C54相位的金属硅化物CoSi2。在低温时Co是主要扩散物,Co进入界面与硅反应,这样Co2Si横向扩散比Si2Ti的小,但是在高温时CoSi转化为CoSi2,硅是主要扩散物。

掺杂类型会对Salicide的阻值产生影响,n型区和p型区的方块电阻是不同。对于n型区,会形成较薄的金属硅化物,所以n型区的方块电阻较大,而p型区的情况相反,所以设计上要区分n型或者p型电阻。

另外杂质在Salicide中的扩散速度非常快,所以在多晶硅中的掺杂物容易进入金属硅化物层,而流串至其他地方。多晶硅会因为掺杂物的流失而产生严重的空乏效应。对于CMOS工艺,则会有p型和n型掺杂物的相互污染,导致MOS晶体管的阈值电压发生改变。

对于65nm以下的Ni-Salicide,首先在低温下形成Ni2Si,随着温度升高再形成NiSi。由于NiSi具有热不稳定性,当温度高于400℃时最终形成稳定的化合物NiSi2,在这个过程中Ni是主要扩散物,导致NiSi2深入衬底形成短路,会形成漏电问题,这种现象称为NiSi侵蚀衬底。为了改善该问题,在Ni靶材中加入5~10%的Pt,也就是利用NiPt的合金靶材代替纯Ni靶材,最终形成NiPt-Salicide。

1.4 SAB工艺技术

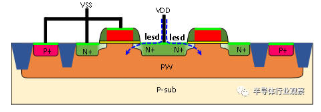

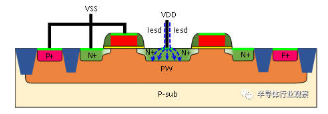

Salicde工艺技术是利用金属与多晶硅和有源区硅反应,同时在多晶硅栅和有源区形成金属硅化物,它是自对准的工艺。虽然金属硅化物可以降低电路的串联电阻,但是金属硅化物对于ESD器件和较高阻抗的电阻是有害的,为了得到相同的电阻阻值,金属硅化物电阻比非金属硅化物电阻需要更多的面积,形成金属硅化物的ESD器件会导致ESD电流在器件表面流动,烧毁ESD器件。如图3-108所示,是ESD电流沿低阻的金属硅化物表面流动,造成发热烧毁器件。如图3-109所示,是在没有金属硅化物的区域,当ESD电流沿有源区某个方向流动,造成该方向硅发热和电阻升高,ESD电流会更倾向于流向电阻低的区域,所以ESD电流会沿有源区各个方向均匀地流动,从而达到保护器件的目的。

图3-108 ESD电流沿金属硅化物表面流动

图3-109 ESD电流沿有源区各个方向流动

为了得到高阻抗的有源区电阻、高阻抗的多晶硅电阻和高性能的ESD器件,需要形成较高阻抗的非金属硅化物区域,通常把这些较高阻抗的区域称为Non-Salicide区域,把这些没有形成金属硅化物的器件称为Non-Salicide器件。为了形成Non-Salicide器件,需要利用金属只会与多晶硅和有源区硅反应而不会与介质层反应的特点,在进行Salicide工艺流程前淀积一层介质层覆盖在Non-Salicide区域,防止这些区域形成Salicide,这种为了形成Non-Salicide器件的技术称为自对准硅化物阻挡层技术(Self-Aligned Block - SAB),也可以称为电阻保护氧化层(Resist Protection Oxide - RPO)。SAB薄膜的材料包括富硅氧化物SRO(Silicon Rich Oxide)、SiO2、SiON和Si3N4。其中,SRO薄膜的硅含量比常规的氧化硅薄膜大,SRO的制备与常规氧化硅大致相同,都可以通过PECVD淀积,气体源是SiH4、O2和Ar。其中SiH4和O2的比率设置成高于形成常规氧化硅所用的比率,另外可以用Si2H6和TEOS(四乙基硅烷)取代SiH4,也可以用N2O或者O3取代O2。淀积SiON的气体源是SiH4、N2O和Ar,淀积Si3N4的气体源是SiH4、N3H和Ar。

为了得到Non-Salicide器件,需要在传统的CMOS工艺流程中增加一道SAB工艺步骤。SAB的工艺流程包括利用PECVD淀积硅化物例如SRO或者SiO2,还有SAB光刻处理(保留Non-Salicide区域光刻胶,去掉Salicide区域光刻胶),以及SAB刻蚀处理(去掉Salicide区域的氧化硅,为下一步形成Salicide做准备)。SAB刻蚀处理包括干法刻蚀和湿法刻蚀。

为什么SAB刻蚀利用干法刻蚀和湿法刻蚀结合呢?因为干法刻蚀是利用带电离子浆轰击的方式去除氧化硅,它既包括物理的轰击也包括化学反应的过程,如果直接用干法刻蚀完全去除氧化硅会损伤衬底硅,导致最终形成的Salicide电阻偏高。而湿法刻蚀是利用化学反应去除氧化硅,不存在物理轰击,所以不会损伤衬底。但是干法刻蚀是各向异性刻蚀,它的刻蚀方向是垂直向下,它能很好地控制尺寸,而湿法刻蚀是各向同性刻蚀,湿法刻蚀横向刻蚀比较严重,不能控制刻蚀的方向,最终刻蚀得到的尺寸会与设计的图形存在偏差,另外横向刻蚀还会渗透到栅氧里面导致漏电,器件失效。所以SAB刻蚀步骤需要干法刻蚀和湿法刻蚀结合。

1.5 SAB和Salicide工艺技术的工程应用

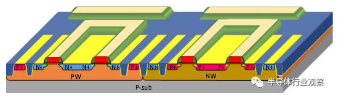

SAB和Salicide工艺技术一般用在深亚微米及其以下的工艺中,为了更好的理解SAB和Salicide工艺技术,下面以纳米级工艺形成ESD器件和Non-Salicide器件为例介绍它们的工程应用。

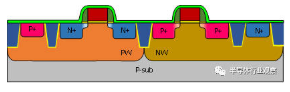

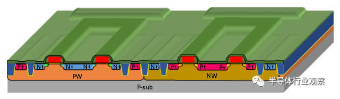

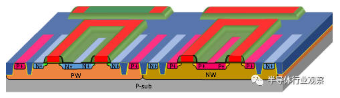

a)选取已经形成重掺杂源漏有源区的工艺流程为起点。如图3-110所示,是形成重掺杂源漏有源区的剖面图。

图3-110 形成重掺杂源漏有源区的剖面图

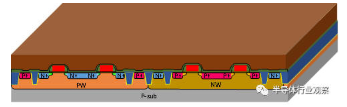

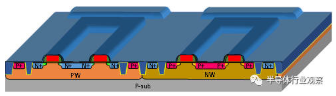

b)淀积SAB。利用PECVD淀积一层SiO2,目的是形成SiO2覆盖在不需要形成金属硅化物(Salicide)的有源区和多晶硅表面,防止它们形成Salicide。如图3-111所示,是淀积SiO2的剖面图。

图3-111淀积SiO2的剖面图

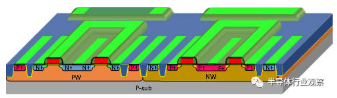

c)SAB光刻处理。通过微影技术将SAB掩膜版上的图形转移到晶圆上,形成SAB的光刻胶图案,非SAB区域上保留光刻胶。如图3-112所示,是涂光刻胶的剖面图。如图3-113所示,是SAB光刻的剖面图。

图3-112涂光刻胶的剖面图

图3-113 SAB光刻的剖面图

d)SAB刻蚀处理。干法刻蚀和湿法刻蚀结合,把没有被光刻胶覆盖的SiO2清除,裸露出需要形成Salicide的有源区和多晶硅,为下一步形成Salicide做准备。如图3-114所示,是SAB刻蚀的剖面图。

图3-114 SAB刻蚀的剖面图

e)去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶。如图3-115所示,是去除光刻胶的剖面图。

图3-115去除光刻胶的剖面图

f)清洗自然氧化层。利用化学溶液NH4OH和HF清除自然氧化层,因为后面一道工艺是淀积NiPt,把硅表面的氧化物清除的更干净,使NiPt跟衬底硅和多晶硅的清洁表面接触,更易的形成金属硅化物,所以淀积NiPt前再过一道酸槽清除自然氧化层。

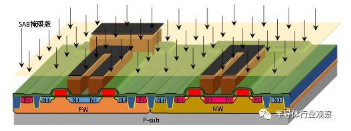

g)淀积NiPt和TiN。利用PVD溅射工艺淀积一层厚度约100Å的NiPt和厚度约250Å的TiN,TiN的作用是防止NiPt在RTA阶段流动导致金属硅化物厚度不一,电阻值局部不均匀。如图3-116所示,是淀积NiPt和TiN的剖面图。

图3-116淀积NiPt和TiN的剖面图

h)第一步Salicide RTA1。在高温约200~300℃的环境下,通入N2使NiPt与有源区和多晶硅反应生成高阻的金属硅化物Ni2PtSi。

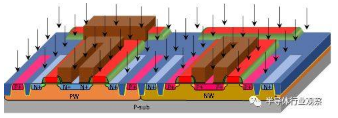

i)NiPt和TiN 选择性刻蚀。利用湿法刻蚀清除TiN和没有与硅反应的NiPt,防止它们桥连造成电路短路。如图3-117所示,是选择性刻蚀的剖面图。

图3-117选择性刻蚀的剖面图

j)第二步Salicide RTA2。在高温约400~450℃的环境下,通入N2把高阻态的Ni2PtSi转化为低阻态的NiPtSi2。